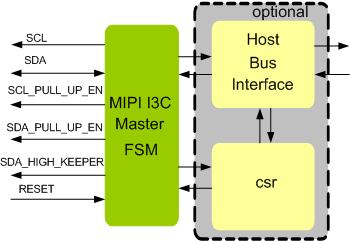

MIPI I3C Master interface provides full support for the two-wire MIPI I3C synchronous serial interface, compatible with MIPI I3C version 1.1 and MIPI I3C HCI version 1.1 specifications. Through its MIPI I3C compatibility, it provides a simple interface to a wide range of low-cost devices. MIPI I3C Master IIP is proven in FPGA environment. The host interface of the MIPI I3C Master can be simple interface or can be AMBA APB, AMBA AHB, AMBA AHB-Lite, AMBA AXI, AMBA AXI-Lite, VCI, OCP, Avalon, PLB, Tilelink, Wishbone or Custom protocol.

MIPI I3C Master IIP IIP is supported natively in Verilog and VHDL

Note: Only mails from offical mail ID will be processed

Request Datasheet Request Evaluation