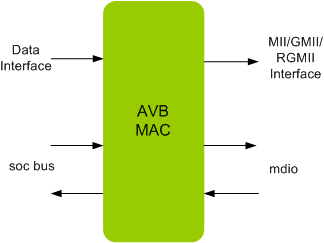

AVB MAC core is compliant with IEEE Standard 802.1Q and IEEE 1722 specification. Through its compatibility, it provides a simple interface to a wide range of low-cost devices. AVB MAC IIP is proven in FPGA environment. It can also supports a variety of host bus interfaces for easy adoption into any design architecture - AHB,AHB-Lite,APB,AXI,AXI-Lite,Tilelink,OCP,VCI,Avalon,PLB,Wishbone or custom buses

AVB MAC IIP IIP is supported natively in Verilog and VHDL

Note: Only mails from offical mail ID will be processed

Request Datasheet Request Evaluation